半導体の性能向上は、これまでムーアの法則に従い、チップ上のトランジスタ密度を2年ごとに倍増させることで達成されてきました。

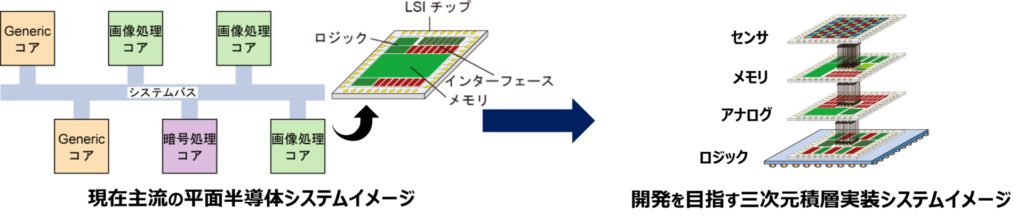

しかし、トランジスタの微細化の限界に近づくにつれ、この法則に従った性能向上が困難になってきました。また、従来の平面システムでは、配線容量や機能複合化などの微細化では解決できない構造上の課題もあります。さらに、微細化は、設備投資が非常に高額となり、新規参入には高い障壁があると考えられます。

半導体の三次元積層技術は、半導体チップを三次元積層接続することで、配線数増加と最短化を達成でき、動作周波数の大幅低減による低消費電力化を実現できると期待されます。

さらに、三次元積層実装技術でメモリ・ロジック等の異なる機能をもつ半導体LSIチップを自由に組合せて活用する新しいアーキテクチャにより、低消費電力化、高機能化、小型軽量化の実現も期待されます。

三次元積層実装は、大手半導体メーカーなど多くの装置・材料メーカーを含む多くの企業が技術開発に力を入れ、メモリなど一部のLSIで実用化されていていますが、ロジックLSI等の量産化には課題があり、いまだ産業化されていません。

平面システムと三次元積層実装LSIとの特徴の差異

| 平面システムの問題点 | 三次元積層実装システムの利点 | |

|---|---|---|

| チップ間の接続距離 | 長い(消費電力大) | 短い(消費電力小) |

| 信号伝達方式 | 少ない信号線のため、高速な信号伝達が必要 (消費電力大) |

超並列バス(データや信号を伝達する回路)の形成(消費電力小) |

| チップの集積効率とアーキテクチャ | チップを集積するほど配線が長くなり、 機能の複合化効率が低い (集積効率低) |

チップの集積効果が高いアーキテクチャとなり、ムーアの法則の限界を超える可能性 (集積効率高) |

| キャパシタへの接続距離 | デカップリング(ノイズ防止)キャパシタへの接続距離が長い (消費電力大、不要輻射の増大) |

デカップリングキャパシタへの接続距離が短い(低消費電力化、不要輻射の低減化) |

| 参入障壁の低さ | 微細化により上記課題を解決するには、設備投資が高額(例:EUV露光装置200~400億円)で、参入企業が限定的 (設備コスト大・国外企業の寡占) |

既存のレガシー設備を生かし、微細化技術と同等以上の高機能LSIを生産。国内企業の参入・技術導入が可能 (設備コスト小・国産化) |